#### CHHATRAPATI SHIVAJI MAHARAJ INSTITUTE OF TECHNOLOGY

Affiliated to the Mumbai University, Approved By AICTE - New Dehli.

DTE Maharashtra (DTE Code: 3477)

St.Wilfred's Education Society, Near Shedung Toll Plaza, Old Mumbai-Pune Highway, Panvel - 410206.

Tel.: 0214 - 239091 / 61. Mob.: +91-92234 34581 / 92244 34581. Email : swc.mumbai@gmail.com

#### 8086 microprocessor Architecture

☐ Subject: Microprocessor

☐ Department : Computer Engineering

☐Year : Second year

☐ Semester : IV

Created By –Er. Revatee Bagade

- 16 bits microprocessor

- 16 bits data bus

- 20 bits address bus

- CISC architecture

- 1 MB physical address space

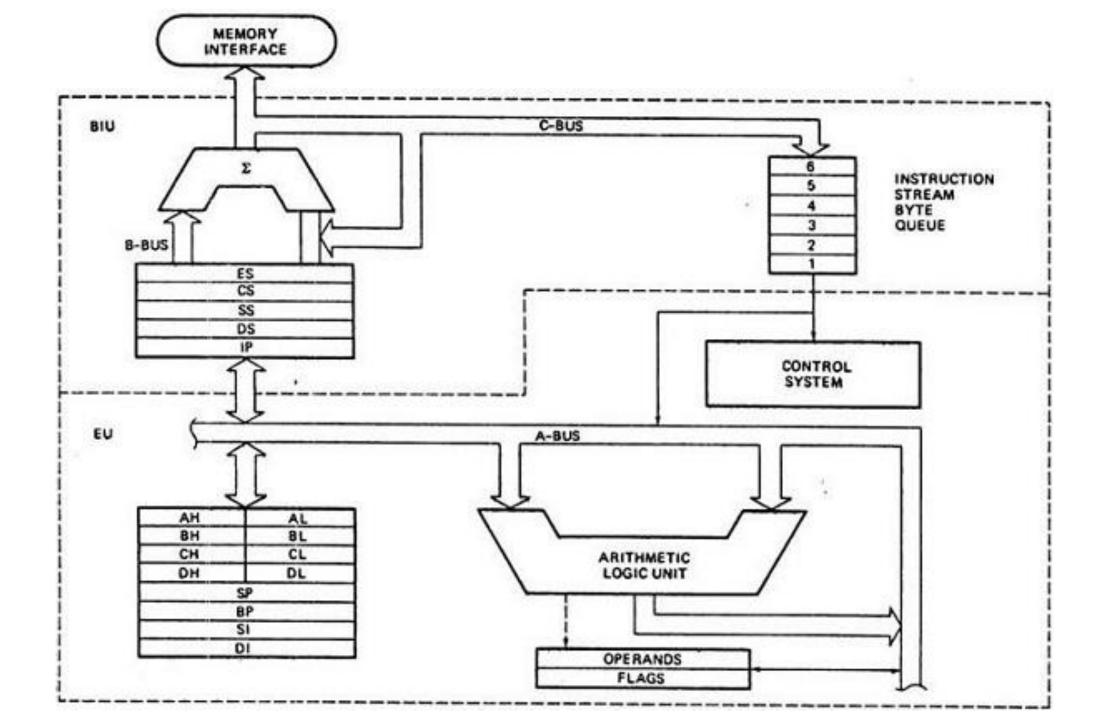

- BIU: Bus Interface Unit.

- Address generating circuit.

- 6 instructions prefetch queue.

- 4 segments of 64 KB of separate I/O space.

- 8 general 16-bit registers.

- EU Execution Unit

- 32-bits ALU

- 8 bit registers paired into 16 bits general purpose register-AX,BX,CX & DX

- Special purpose register- stack pointer, base pointer, source index & destination index

- 40 pins dual in line package.

- High speed.

- Powerful instruction set.

- 2 operating modes- minimum mode and maximum mode.

- It can support 64k I/O ports.

- Memory segmentation

- Memory banking

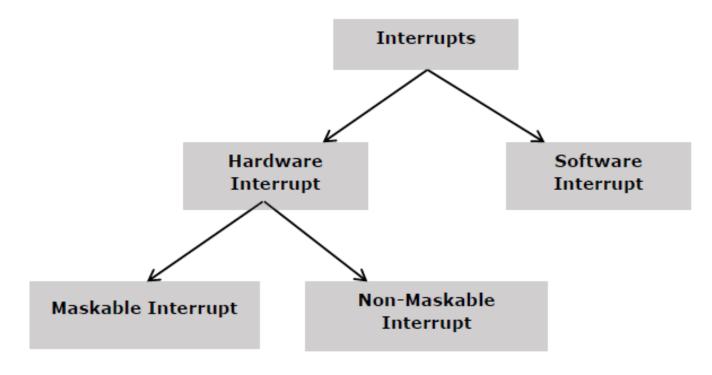

- 2 hardware interrupts- NMI & INTR

- 256 software interrupts

| Aspect               | Non-Maskable Interrupt (NMI)                                                                                                | Interrupt (INTR)                                                                                                                                |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Triggering Factor    | Caused by critical hardware failures or exceptional conditions that require immediate attention                             | Initiated by external hardware devices or software instructions based on specific events or conditions                                          |

| Priority             | Higher priority than INTR, cannot be disabled or masked                                                                     | Lower priority compared to NMI, can be disabled or masked                                                                                       |

| Purpose              | Typically used for handling critical system errors or emergencies, such as power failure detection or hardware malfunctions | Used for handling regular events or tasks, such as I/O operations or timer events                                                               |

| Response Time        | Immediate response is expected to address critical issues                                                                   | Response may vary based on the priority of the interrupt and the current processor state                                                        |

| Masking and Handling | Cannot be disabled or masked, usually directly handled by dedicated hardware                                                | Can be disabled or masked temporarily to prioritize other tasks, handled by the interrupt controller and processor interrupt handling mechanism |

| Examples             | Power failure, memory parity errors, hardware malfunctions                                                                  | Keyboard input, timer overflow, I/O device request                                                                                              |

Mark Wen.